risc-v

Risc-V Simple Learning

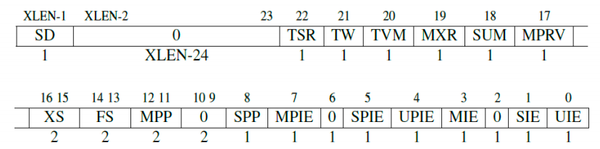

原文链接:https://ovea-y.cn/risc_v_simple_learning/ 诞生原因 * x86指令集爆发性增长 * 由于非商业,所以不会受到随意的更改 * 没有历史包袱 * 例如x86还保留着BCD数据格式的操作指令,占据了操作码空间的1.6%(4/256) * 模块化的ISA(核心是RV32I),可以根据自己的需求进行选择 * x86由于是增量式的ISA,因此每次带有新指令的CPU必须也要实现旧指令。 * 简介的ISA,相比其他RISC架构指令集,实现同一功能可以进行更少的指令执行 RV32/RV64的特权架构 机器模式(M) 机器模式是risc-v中的最高权限模式,具有对裸机的完整控制权,是所有RISC-V处理器必须实现的权限模式。 特性 * 拦截 * 异常处理 * 同步异常(指令执行期间产生的,例如执行了不合规范的指令,或者访问了错误的内存地址等) * 访问错误异常 当物理内存地址不支持访问时(比如写入ROM) *